隨著FPGA和CPLD技術(shù)的飛速發(fā)展,軟核處理器在嵌入式系統(tǒng)設(shè)計(jì)中的地位日益重要。其中,NIOS II作為Altera(現(xiàn)Intel FPGA)推出的經(jīng)典軟核處理器,以其靈活性和可定制性,在FPGA、CPLD乃至ASIC設(shè)計(jì)中廣受青睞。本文結(jié)合電子技術(shù)論壇中的熱門(mén)討論,特別是“小炮與鋯石9”軟核學(xué)習(xí)案例,深入探討NIOS II硬件框架結(jié)構(gòu),幫助開(kāi)發(fā)者更好地掌握這一關(guān)鍵技術(shù)。

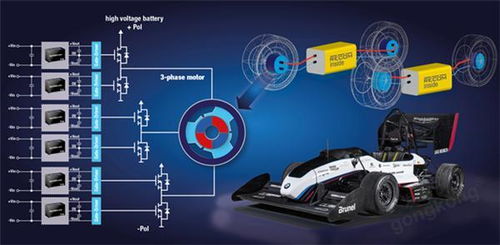

NIOS II處理器是一個(gè)基于RISC架構(gòu)的軟核,它允許用戶根據(jù)具體應(yīng)用需求定制指令集、外設(shè)和內(nèi)存接口。其硬件框架主要包括以下核心組件:處理器核心、總線系統(tǒng)(如Avalon總線)、中斷控制器、定時(shí)器、以及用戶自定義外設(shè)。在“小炮與鋯石9”學(xué)習(xí)項(xiàng)目中,學(xué)習(xí)者通過(guò)實(shí)際搭建NIOS II系統(tǒng),驗(yàn)證了其模塊化設(shè)計(jì)的優(yōu)勢(shì),例如通過(guò)Avalon總線輕松集成UART、SPI等外設(shè),實(shí)現(xiàn)高效的片上系統(tǒng)(SoC)設(shè)計(jì)。

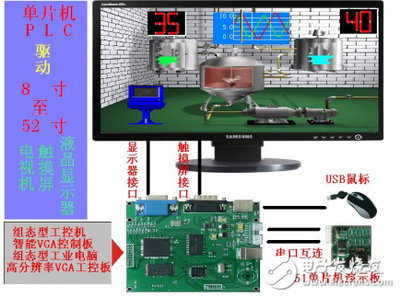

NIOS II的深入學(xué)習(xí)離不開(kāi)對(duì)FPGA和CPLD平臺(tái)的熟悉。在電子技術(shù)論壇上,許多開(kāi)發(fā)者分享了使用Intel Quartus等工具進(jìn)行NIOS II軟核配置的經(jīng)驗(yàn)。例如,在鋯石9開(kāi)發(fā)板上,用戶可以通過(guò)QSYS工具快速構(gòu)建硬件系統(tǒng),定義處理器參數(shù)和總線連接,然后使用Nios II Software Build Tools (SBT) 編寫(xiě)和調(diào)試軟件代碼。這種軟硬件協(xié)同設(shè)計(jì)方法,不僅提升了開(kāi)發(fā)效率,還降低了ASIC原型設(shè)計(jì)的門(mén)檻。

NIOS II框架的靈活性使其適用于多種應(yīng)用場(chǎng)景,從簡(jiǎn)單的控制任務(wù)到復(fù)雜的數(shù)據(jù)處理。論壇中,有用戶通過(guò)“小炮”項(xiàng)目實(shí)現(xiàn)了實(shí)時(shí)信號(hào)處理系統(tǒng),展示了NIOS II在性能優(yōu)化和資源管理方面的能力。與ASIC設(shè)計(jì)結(jié)合時(shí),NIOS II可以作為驗(yàn)證核心,幫助測(cè)試定制邏輯的功能,這在專(zhuān)業(yè)電子論壇上被廣泛討論為“軟硬結(jié)合”的最佳實(shí)踐。

NIOS II硬件框架結(jié)構(gòu)的學(xué)習(xí)是FPGA/CPLD開(kāi)發(fā)者的重要課題。通過(guò)論壇交流和實(shí)際項(xiàng)目如“小炮與鋯石9”,開(kāi)發(fā)者可以深入理解其架構(gòu)細(xì)節(jié),提升電子技術(shù)開(kāi)發(fā)水平。隨著人工智能和物聯(lián)網(wǎng)的興起,NIOS II等軟核技術(shù)將繼續(xù)在專(zhuān)業(yè)電子領(lǐng)域發(fā)揮關(guān)鍵作用,推動(dòng)創(chuàng)新應(yīng)用的實(shí)現(xiàn)。